International Journal for Modern Trends in Science and Technology Volume 11, Issue 05, pages 1248-1254

ISSN: 2455-3778 online

Available online at: http://www.ijmtst.com/vol11issue05.html

DOI: https://doi.org/10.5281/zenodo.15546042

# A High-Linearity Blocker-Tolerant Cascode LNA for WiFi and IoT Devices

#### S. Mohan Das 1, Dr Kota Venkata Ramanaiah 2

<sup>1</sup>Research Scholar, Electronics and Communication Engineering, YSR Engineering College of Yogivemana University, Korrapadu Road, Proddatur – 516360, YSR District, Andhra Pradesh, India.

<sup>2</sup>Professor, Electronics and Communication Engineering, YSR Engineering College of Yogivemana University, Korrapadu Road, Proddatur – 516360, YSR District, Andhra Pradesh, India.

### To Cite this Article

S. Mohan Das & Dr Kota Venkata Ramanaiah (2025). A High-Linearity Blocker-Tolerant Cascode LNA for WiFi and IoT Devices. International Journal for Modern Trends in Science and Technology, 11(05), 1248-1254. https://doi.org/10.5281/zenodo.15546042

## **Article Info**

Received: 01 May 2025; Accepted: 26 May 2025.; Published: 29 May 2025.

**Copyright** © The Authors; This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

#### **KEYWORDS**

high gain, low noise amplifier, metal oxide semiconductor field effect transistor, noise figure, radio frequency)

# **ABSTRACT**

In the field of modern wireless communication systems, designing Low-Noise Amplifiers (LNA) is essential to attaining increased signal sensitivity and overall system effectiveness as well as reducing noise inputs from later phases. Furthermore, in portable applications, the low noise figure (NF) and high gain are essential LNA performance criteria. Typically, LNA has problems with bandwidth, gain, stability, amplification, and noise performance. The right transistor selection, balanced impedance calibration, bias optimization, and circuit fine-tuning are necessary to overcome these obstacles. Furthermore, because of their superior noise performance, high input impedance, complementary metal-oxide semiconductor (CMOS) integration capabilities, low power operation, and suitability for a variety of frequency applications, metal oxide semiconductor field effect transistors (MOSFETs) are a common option in LNA design. The LNA exhibits exceptional linearity, amplification, and Noise Figure over a specified frequency range through simulation and continuous improvement. By developing a method for LNA construction that balances competing requirements and reveals efficient noise reduction strategies, this invention advances radio frequency (RF) circuitry. The results highlight how crucial a carefully considered circuit design and parameter tuning are to achieving exceptional LNA capabilities, making it suitable for integration into a variety of communication systems that require low noise and high sensitivity.

#### 1. INTRODUCTION

This Advanced wireless communication techniques for high-resolution radars led to a significant increase in the need for millimeterwave transceivers and high data rates, which have received a lot of interest from both academic and industrial sectors<sup>1,2</sup>. This leads to the conclusion that the most crucial parts millimeter-wave transceivers are LNA, which includes radiometry for earth science, passive connections for remote sensing, receivers for communication, transistors for radar instruments, and radio astronomy units. Because of this, the LNA is selected as a first step and a key element for processing the performance based on wireless system sensitivity<sup>2</sup>. Since it receives the weak signal from the entire Ultra-wideband (UWB) and offers a sufficient signal-to-noise ratio for the signal process, the LNA is an important part of the transceiver system; As a result, the entire UWB band has a flat and enough power gain, acceptable input impedance matching, and a low noise figure (NF)3. Several methods have been developed for the design of UWB LNAs.

In particular, LNA maintains low NF, which, in addition to process, voltage, and temperature dissimilarity, is in charge of increasing the production of high and flat gain with the amplification of low input (RF) signals, less power consumption, chip area, high linearity, stability, and robustness<sup>4</sup>. These days, HEMT's cryogenic-based cooling method is widely employed due to its ability to reduce noise and enhance the sensitivity of radiometers in the fields of astrophysics and Earth-observing equipment<sup>5,6</sup>. In many applications requiring extremely sensitive receivers, cryogenically chilled microwave LNA is essential<sup>7,8</sup>. Therefore, in order to function at the desired levels, conventional cryogenic LNAs currently require a minimum of 4 mW of direct current (dc) power<sup>9,10</sup>.

Wideband communication has been utilized for a variety of applications, including current-reused designs<sup>12</sup>, Wideband matching using input band-pass filters (IBPF)<sup>11</sup>, setups for distributed amplifiers and resistive feedback systems. However, each of these methods has drawbacks when it comes to meeting better criteria<sup>13</sup>.

#### II. LITERATURE SURVEY

Using LNA, David Fritsche et al<sup>1</sup> created 60 GHZ for a low-volume CMOS process at 28 nm. Additionally, the

system presents a revolutionary method for creating an ideal RF transistor layout, transmission line design, and high Q-capacitor implementation in order to create a high frequency design with the active and passive devices. When compared to existing systems, the LNA performs better.

An inventive ultra-wideband LNA design with twin cross-coupled capacitors and a special gain flattening method was presented by Saeed Ghaneei Aarani et al<sup>13</sup>. This LNA is implemented using the 0.18-um RF CMOS technology in a cascade common-gate topology. To improve the NF, the design adds a unique cross-coupled capacitor and a disparity cascode.

Shirin Montazeri et al<sup>14</sup> developed a cryogenic SiGe LNA technique based on 2–4 GHZ and applied it to the Tower Jazz SBC18H3 instruments. The lowest recorded rate that includes a low power oscillation is used to assess the temperature level of noise. Nonetheless, a cryogenic SiGe LNA would require little power to run with a DC power consumption of only 3mw<sup>12</sup>.

In order to achieve a pole-converging effect and wideband performance, Cheng Cao et al<sup>15</sup> proposed a CMOS pole-converging triple-cascode LNA in which a pole-converging capacitor is integrated between the common-gate stage's gate and drain nodes. To achieve good input matching and a low NF, the triple-cascode design used the modified broadband simultaneous noise and input-matching technique.

# III. MOTIVATION

Reducing the intrinsic noise produced by the amplifier is crucial to obtaining a respectable increase in signal power while preserving a reasonable S/N at the LNA's output. NF, which measures the drop in S/N from the input to the end of the element, becomes a crucial metric for evaluating the radio performance of the communication system.

A holistic approach, marked by interaction and refinement throughout the stages, is preferred over seeing and setting the RF chain as distinct entities. Given its significant impact on the noise characteristics of the entire system, a preamplifier with an extraordinarily low NF is frequently required in receiver applications, especially when it is used as the first stage of the receiver front end.

#### A.LNA Overview

In order to increase the strength of signals coming from weak sources, amplifiers are essential. LNAs are useful for picking up and enhancing weak signals coming from far-off sources, which could include satellites or even stationary or mobile transmitters. To standardize many aspects like gain, noise figure, linearity, and power efficiency, several strategies have been developed for LNA design, including the differential cascode topology, layered structure, body biasing, active inductor, transformer-based feedback, and current reuse.

# B. Approach to LNA Design

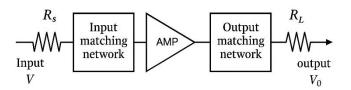

Three stages are integrated in the LNA: input matching, amplification, and output matching. The input section provides a good input reflection coefficient without distortion, the amplifier section provides adequate gain, and the output stage, at the end, provides a good output reflection coefficient and removes noise.

The internal components of the amplifier, each painstakingly designed for a specific purpose, determine how well it operates.

Therefore, defining the amplifier's architecture means identifying the most crucial components, namely the transistors, and coming up with equations that specify its operation.

However, some transistors may interfere with or intensify the effects of their counterparts, creating challenging problems for the designers to resolve.

The first part of the receiver sides in the LNA, which reduces the amount of noise introduced while boosting the incoming signal power from the antenna.

The identical LNA that is shown in Fig.1 also illustrates this noise-reduction feature.

Fig.1. System-Level Block Diagram for LNA Implementation

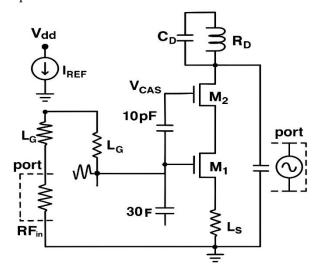

C.LNA Equivalent Circuit with MOSFET Implementation

The MOSFET schematic diagram with LNA, both AVSS, and AVDD coupled to the two MOSFET switches of M<sub>1</sub> and M<sub>2</sub>, which contain gate, drain, and source connections, is shown in Figure 2. Along with a 5 pF

capacitor C<sub>3</sub> inductor L<sub>2</sub> and a 300pF capacitor C1C, port 0 makes it easier to connect to the gate and source terminals of the M<sub>1</sub> switch. This combination also includes L<sub>11</sub> and is grounded at the voltage level V<sub>dc</sub>, which is equal to V<sub>dd</sub>, V<sub>1</sub>, and V<sub>7</sub>. Conversely, the M<sub>1</sub> switch's drain terminal is connected to the M<sub>2</sub> switch's source side in a complex manner, along with a resistor R<sub>1</sub> with a value of  $400\Omega$  (r), an inductor L<sub>13</sub>, and a capacitor C<sub>0</sub>.

Fig.2. LNA schematic drawing with MOSFET.

The amplifier circuit was unique within the microwave computer program ADS, which serves as a platform for careful testing and optimization of its performance within the designated frequency spectrum. In this case, the LNA runs under the low supply voltage of 0.55V. Improved response characteristics can be obtained by optimizing the matching networks' component values, which are then adjusted for real-world use. Figure 2 is an artistic representation of the entire amplifier track, including the necessary DC bias circuitry. This diagram clearly shows how all component values parameters, synchronized with standardized purposeful tactic used to simplify the process of implementation.

# D. Equations

Common source switch  $M_1$

$$A_v = -g_m(R_L || r_0) \tag{1}$$

where  $A_v$  is the transfer from gate G to drain D or the gain,  $r_0$  is the resistance output, and  $R_L$  denotes the load resistor. At this point, the  $M_1$  switch generates a high frequency of transit  $f_t$  and transconductance  $g_m$ .

Common gate switch  $M_2$

$V_{cas}$  functions as a current buffer by operating as a small-signal system with input via the source and output via the drain; ideally, a high resistivity  $r_0$  (output impedance) is desired.

#### E. LNA MOSFET Selection

The Selecting the right MOSFET for the LNA requires careful evaluation of a number of variables. These variables include things like the MOSFET's power handling capability, input and output impedance matching, NF, and transconductance efficiency.

# 1) Noise Figure:

A number of considerations are taken into consideration while choosing MOSFETs for a circuit. Important factors to take into account are the NF and high transition frequency, or speed, which are closely related and directly proportional to the transition frequency. Examples of how technology scaling improves the transition frequency are 90 nm at 100 GHz and 65 nm at 120 GHz.

# 2) Common source LNA noise factor:

A common-source LNA's noise factor describes how well it can maintain the quality of a weak input signal while reducing the amount of noise that enters the output. This quantity, which is frequently expressed in decibels (dB), measures the extra noise the amplifier adds and contrasts it with the lowest amount of noise that the input signal may theoretically produce. Better noise performance is shown by a lower noise factor, which suggests that the LNA amplifies the intended signal well with little extra noise.

The following formula represents the noise factor, which is defined as the ratio of effective input noise power to noise input from source resistance:

$$F = 1 + \frac{R_L}{R_S} + \frac{R_g}{R_S} + \delta \phi g d_0 R_S \left(\frac{\chi_0}{\chi_t}\right)^2 \tag{2}$$

Fstands for frequency,  $R_S R_g$  for source and gate ohmic resistance, and  $R_l$  for load resistor.

#### 3) Quality factor:

When discussing LNA with MOSFETs, the phrase "quality factor" frequently refers to the inherent quality factor, or Q-factor, of the transistor. The transistor's behavior inside a specific frequency range is described by the Q-factor. It has a direct effect on the LNA's performance and is an important parameter in RF circuit intent.

Noise Figure

$$\propto \frac{1}{Q}$$

(3)

# IV. SPECIFICATIONS FOR TARGETTED LOW-NOISE AMPLIFIERS

A targeted LNA is a specialized amplifier that is engineered to predetermined precisely meet performance objectives for signal quality preservation, gain improvement, and noise reduction. This that method guarantees the LNA customized successfully satisfies the needs of a certain system or A tailored LNA maximizes application. amplification of weak signals while reducing additional noise by concentrating on particular frequency ranges, NF parameters, and gain levels.

Gain = 20 dB: According to this specification, the LNA is made to provide a gain of 20 dB (dB). It shows the amplifier's amplification factor, or the ratio of the output to the amplitude of the input signal. The input signal is amplified by 20 dB in this instance by the LNA.

The power dissipation of the LNA, or the quantity of electrical power used by the amplifier while it is operating, is specified in this standard as 9 mW. The LNA in this instance uses nine milliwatts (mW) of power.

Input Isolation: usually describes the LNA's capacity to separate its input from undesired signals or interference sources.

Output Impedance: The LNA's output port impedance is specified by its output impedance. Matching the LNA to later circuit stages or antennas requires this information.

Reverse Volume Gain: The table doesn't include a value or an explanation for this parameter, and reverse volume gain is not a typical LNA specification. It might be a reference to a unique or application-specific measure.

The input power level at which the amplifier's output power drops by 1 dB (about 10%) from its linear gain value is known as 1 dB compression, or P1dB. Understanding the linearity and distortion characteristics of the amplifier requires knowledge of this specification.

Intercept Point: The linearity of an amplifier is described by its intercept points. The third-order and second-order intercept points are two frequently used intercept points in radio frequency applications. These points show the input power levels at which particular intermodulation or harmonic distortion products achieve particular thresholds.

Technology: 65nm. The semiconductor technology node where the LNA is produced is indicated by this specification. In this instance, a 65-nm (nm) process expertise is used to create a fake LNA.

#### V. SIMULATION RESULTS

The NF, gain, S-parameters, and harmonic balancing of the LNA were all simulated and examined using the ADS program. It is essential to evaluate the stability parameter before exploring these facets. At a frequency of 2.4 GHz, the stability constant k, which characterizes the circuit's stability, is found to be 1.615.

# A. The parameters of the simulation

The desired values of LNA with gain, power dissipation, input isolation, output impedance, reverse volume gain, 1 dB compression, intercept point, and technology with designated values were listed in Table 1.

# B. LNA input return loss

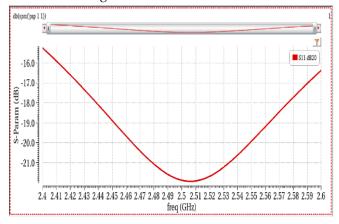

Simulations within the Cadence Specter analog design environment (ADE) are used to generate S-parameters, analyze NF, evaluate stability, and test linearity. The two-stage forward body bias technique was used at a frequency of 2.5 GHz to produce the simulated results. The circuit draws a total current of 820  $\mu$ A while maintaining full operation at a supply voltage of 0.55 V. Both the pre- and post-layout findings for S11 are shown in Figure 3.

Fig.3. LNA input return loss.

TABLE I. TARGET SPECIFICATIONS FOR THE LOW NOISE AMPLIFIER (LNA)

| S<br>No | Specifications          | Value                              |

|---------|-------------------------|------------------------------------|

| 1       | Gain $A_v$              | 20 dB                              |

| 2       | Power Dissipation = 9mW | $V_{DD} = 1V $ and $I_D = 9mA$     |

| 3       | Input Isolation         | $S_{11} = \frac{V_1}{I_1} < -10dB$ |

| 4 | Output Impedance     | $S_{22} = \frac{V_2}{I_2} < -10  dB$ |

|---|----------------------|--------------------------------------|

| 5 | Reverse Voltage Gain | $S_{12} = \frac{V_1}{2} < -30dB$     |

| 6 | 1 dB Compression     | $P_{1dB} = -5dBm$                    |

| 7 | Intercept point      | IIP3 = -15dBm                        |

| 8 | Technology           | 65nm                                 |

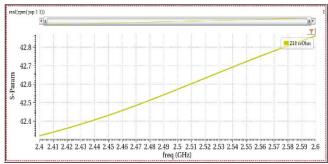

# C.LNA input impedance

Figure 4 shows a comparison of the simulation results for the input of the LNA impedance between the desired input impedance (Zin = 50  $\Omega$ ) and the obtained value (42.6  $\Omega$ ) at a frequency of 2.5 GHz. Optimizing signal transfer and power matching between the source and the LNA depends heavily on the input impedance, which is the complex component of voltage to current at the input port. The intended input impedance of 50  $\Omega$  in this case denotes the perfect impedance match for effective power transfer and low signal reflection.

The obtained input impedance of 42.6  $\Omega$  at 2.5 GHz, however, somewhat differs from the desired value.

Fig.4. LNA input impedance

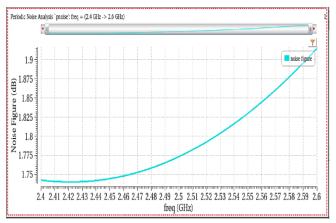

#### D. LNA noise figure

As shown by their portrayal on the Smith chart, NF and gain, two elements that frequently entail a trade-off in LNA design are the main focus of the first simulation. It is generally uncommon to achieve both the maximum gain and the smallest NF at the same impedance condition. As a result, choosing a combination that matches the intended gain and NF at a certain impedance state becomes essential. The input and output stability must be considered equally when calculating the impedance state value. The system as a whole is still completely stable. The LNA NF simulation's outcomes demonstrate a noteworthy accomplishment. The simulation exhibits an amazing NF of 1.775 dB at a frequency of 2.5 GHz, with an intended NF of 2 dB.

Fig.5. LNA Noise figure

This result highlights how well the LNA design reduces noise and improves overall signal-to-noise efficiency at the designated frequency. Figure 5 shows a graphic representation of the LNA noise figure.

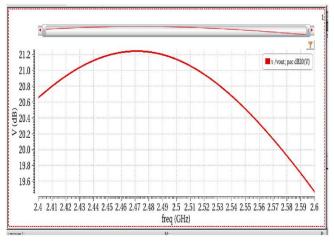

#### E. LNA Gain

Fig.6 illustrates how LNA gains offer important information about the circuit's amplification capabilities. A key parameter that represents the output to the input signal amplitude is gain. It shows how well the LNA can amplify weak input signals without adding undue distortion or noise. When it comes to LNA gain simulation results, these data usually show how the gain fluctuates throughout the intended frequency range. On a graph, gain is typically displayed on the y-axis and frequency on the x-axis. A circuit resonance is produced by the gain frequency response, which is depicted in Fig.6 and has bandwidth characteristics over the relative constant of deviation.

Fig.6. LNA Gain

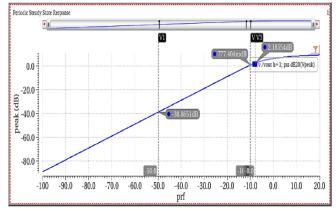

#### F. P1dB Compression Point

According to the simulation findings, the P1dB compression point is reached at a gain of 2.185 dB, as shown in Fig.7. Interestingly, the difference between the

ideal output voltage and the practical gain or output voltage is 1 dB.

Fig.7. P1dB Compression Point.

This is the moment at which non-linear distortion starts to dominate the amplifier's response and the key juncture where the output power of the amplifier starts to diverge by 1 dB from its linear behavior. idB compression is the difference of 1 dB between the ideal output voltage or practical gain and the output voltage. According to the findings, there is a 1 dB discrepancy between the ideal output voltage and practical gain or output voltage at 2.185 dB.

# VI. CONCLUSION

A novel LNA design methodology using MOSFET switches is proposed in this paper. The field of wireless communication receptors has advanced rapidly over the past several generations, making impressive progress in the present environment. One crucial design factor is the fundamental structure of low-noise sensors. Within this paradigm, the LNA's configuration which is optimized for increased efficacy is of significant relevance. An inductive degradation network is preferred in order to implement this model, resulting in a low NF of 0.95 dB, a strong power gain of 17 dB, and excellent linearity. Because of its cleverly designed LNA, it may be used for wireless receiver utilities like wireless LAN in the 2.44 GHz central frequency domain.

# Conflict of interest statement

Authors declare that they do not have any conflict of interest.

# REFERENCES

[1] Fritsche D, Tretter G, Carta C, Ellinger F. Millimeter-wave low-noise amplifier design in 28-nm low-power digital CMOS.

- IEEE Trans Microwave Theory Techniques. 2015;63(6):1910-1922. doi:10.1109/TMTT.2015.2427794

- [2] Yu Y, Liu H, Wu Y, Kang K. A 54.4–90 GHz low-noise amplifier in 65-nm CMOS. IEEE J Solid-State Circuits. 2017;52(11):2892-2904. doi:10.1109/JSSC.2017.2727040

- [3] Li N, Feng W, Li X. A CMOS 3–12-GHz ultrawideband low noise amplifier by dual-resonance network. IEEE Microwave Wirel Components Lett. 2017;27(4):383-385. doi:10.1109/LMWC.2017.2679203

- [4] Saberkari A, Kazemi S, Shirmohammadli V, Yagoub MC. Gm-boosted flat gain UWB low noise amplifier with active inductor-based input matching network. Dermatol Int. 2016;52:323-333. doi:10.1016/j.vlsi.2015.06.002

- [5] Leong KM, Mei X, Yoshida W, et al. A 0.85 THz low noise amplifier using InP HEMT transistors. IEEE Microwave Wirel Components Lett. 2015;25(6):397-399. doi:10.1109/LMWC.2015.2421336

- [6] Lee JH, Lin YS. 3.88 dB NF 60 GHz CMOS UWB LNA with small group-delay-variation. Electron Lett. 2013;49(7):472-474. doi:10.1049/el.2012.4455

- [7] Varonen M, Reeves R, Kangaslahti P, et al. An MMIC low-noise amplifier design technique. IEEE Trans Microwave Theory Techniques. 2016;64(3):826-835. doi:10.1109/TMTT.2016.2521650

- [8] Kargaran E, Madadi B. Design of a novel dual-band concurrent CMOS LNA with current reuse topology. In: 2010 international conference on networking and information technology. IEEE; 2010;386-388.

- [9] Murad SAZ, Azizan A, Hasan AF. Ultra-low power 0.45 mW 2.4 GHz CMOS low noise amplifier for wireless sensor networks using 0.13-μ m technology. Bull Electric Eng Informatics. 2020;9(1):396-402. doi:10.11591/eei.v9i1.1852

- [10] Tulunay G, Balkir S. A synthesis tool for CMOS RF low-noise amplifiers. IEEE Trans Comput-Aided des Integr Circuits Syst. 2008;27(5): 977-982. doi:10.1109/TCAD.2008.917579

- [11] Regulagadda SS, Sahoo BD, Dutta A, Varma KY, Rao VS. A packaged noise-canceling high-gain wideband low noise amplifier. IEEE Trans Circuits Syst II Express Briefs. 2018;66(1):11-15. doi:10.1109/TCSII.2018.2828781

- [12] Moy T, Huang L, Rieutort-Louis W, et al. An EEG acquisition and biomarker-extraction system using low-noise-amplifier and compressive-sensing circuits based on flexible, thin-film electronics. IEEE J Solid-State Circuits. 2016;52(1):309-321. doi:10.1109/JSSC. 2016.2598295

- [13] Aarani SG, Hayati M, Kazemi AH. A novel UWB low-noise amplifier design using double capacitor cross-coupled feedback. AEU Int J Electron Commun. 2019;104:1-9. doi:10.1016/j.aeue.2019.03.007

- [14] Montazeri S, Bardin JC. A 2–4 GHz silicon germanium cryogenic low noise amplifier MMIC. In: 2018 IEEE/MTT-S international microwave symposium-IMS. IEEE; 2018:1487-1490.

- [15] Cao C, Li Y, Wang Z, et al. CMOS X-band pole-converging triple-cascode LNA with low-noise and wideband performance. IET Circuits Devices Syst. 2022;16(1):26-39. doi:10.1049/cds2.12081.