International Journal for Modern Trends in Science and Technology

Volume 11, Issue 05, pages 774-776

ISSN: 2455-3778 online

Available online at: http://www.ijmtst.com/vol11issue05.html

DOI: https://doi.org/10.5281/zenodo.15335152

# Efficient Fast Mapping and Updating Algorithms for Binary Content Addressable Memory (CAM) on FPGA

Dr.K.H.Shakthi Murugan, Sk.Mahaboob Roshan, D.Tharun, U.Yeswanth, CH.Sunil

Department of Electronics and Communication Engineering, Narayana Engineering College, Gudur, Andhra Pradesh, India.

## To Cite this Article

Dr.K.H.Shakthi Murugan, Sk.Mahaboob Roshan, D.Tharun, U.Yeswanth & CH.Sunil (2025). Efficient Fast Mapping and Updating Algorithms for Binary Content Addressable Memory (CAM) on FPGA. International Journal for Modern Trends in Science and Technology, 11(05), 774-776. https://doi.org/10.5281/zenodo.15335152

# **Article Info**

Received: 03 April 2025; Accepted: 27 April 2025.; Published: 02 May 2025.

**Copyright** © The Authors; This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

# **KEYWORDS**

# **ABSTRACT**

Content Addressable Memory (CAM), FPGA, Binary CAM (BCAM)

Content Addressable Memory (CAM) is a specialized form of memory designed for high speed data retrieval by matching content rather than memory addresses. It is extensively used in applications such as networking, data compression, and artificial intelligence for its rapid parallel search capabilities. However, traditional CAM implementations face several limitations, including high power consumption, limited scalability, and latency during updates. This project introduces efficient fast mapping and updating algorithms for Binary CAM (BCAM) implemented on FPGA platforms. By leveraging parallel processing techniques and reconfigurable architecture, the proposed system reduces search latency and enhances throughput. The model incorporates advanced mapping algorithms to optimize memory utilization and minimize power consumption.

## 1. INTRODUCTION

Content Addressable Memory (CAM) is a specialized form of memory used for fast data searching and matching operations. Unlike conventional memory, which retrieves data based on specific addresses, CAM enables parallel comparison of stored data against input data, making it highly effective for real-time applications. CAM is widely used in networking for IP address lookup, packet classification, and data filtering. Its rapid parallel search capabilities make it essential for high-speed systems. However, traditional CAM

architectures suffer from certain drawbacks, including high power consumption, limited scalability, and slow updating mechanisms. To address these challenges, modern systems are shifting towards Field Programmable Gate Arrays (FPGAs)for implementing Binary CAM (BCAM) architectures. FPGAs offer reconfigurability, parallel processing, and lower power consumption, making them an ideal platform for high speed CAM designs. This project proposes an efficient BCAM model on FPGA, incorporating advanced mapping and updating algorithms. The fast mapping

technique accelerates the search process by optimizing memory utilization, while the updating algorithm reduces latency by enabling quick modifications without significant performance degradation. The model leverages FPGA's reconfigurable architecture to achieve improved throughput and power efficiency.

## II. PROPOSED SYSTEM

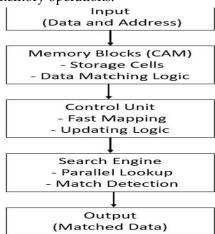

In our proposal, we present a he proposed BCAM model introduces a hybrid algorithm combining fast mapping with optimized updating for improved performance. This section explains the architecture and working of the proposed system in detail.fig(1) input, memory blocks, control unit, search engine, and output. The input module receives the data and address for storage or search operations. The memory blocks contain the storage cells and data matching logic, performing parallel search operations efficiently. The control unit manages fast mapping and updating algorithms, ensuring dynamic data handling. The search engine performs parallel lookup operations, accelerating the matching process. Finally, the output module displays the matched data or address, enabling quick and efficient data retrieval. This architecture enhances performance by reducing search latency and optimizing power consumption, making . Overall, the introduction of fast mapping and efficient updating algorithms in BCAM on FPGA enhances performance, reduces power usage, and offers a scalable solution for high-speed puv memory operations.

Fig 1: block diagram of proposed system

fig(1) input, memory blocks, control unit, search engine, and output. The input module receives the data and address for storage or search operations

### III. IMPLEMENTATION

Implementation of the Proposed BCAM Model on FPGA The implementation of the Binary Content Addressable Memory (BCAM) on FPGA follows a structured design process to optimize performance, reduce latency, and improve power efficiency. The design is developed using Verilog HDL and synthesized using Xilinx Vivado. implementation involves defining structures, developing search and update algorithms, and optimizing hardware resources. Architecture of the Model The architecture of the proposed BCAM consists of multiple functional blocks working together to ensure efficient data storage, retrieval, and updating. The key components include: 1. Input Module - Receives the data and address for storage or search operations. 2. Memory Blocks (CAM) - Stores binary content and performs parallel search operations. 3. Control Unit -Manages fast mapping and updating algorithms. 4. Search Engine - Executes parallel search operations for rapid data retrieval. 5. Output Module - Displays matched addresses or retrieved data.

# Layers of the Model

The BCAM model is designed in a layered approach for modularity and efficient processing:

- 1. Physical Layer:

- o Represents the hardware implementation on the FPGA.

- o Includes logic gates, flip-flops, and memory cells for data storage.

- 2. Processing Layer:

- o Executes search, mapping, and update operations.

- o Handles fast comparison using parallel processing techniques.

- 3. Control Layer:

- o Manages communication between memory blocks and processing units.

- o Implements algorithms for efficient memory utilization.

- 4. Application Layer:

- o Interfaces with external systems for input and output.

- o Supports integration into networking, AI, and database applications.

### APPLICATIONS

The BCAM model on FPGA is widely used in networking for fast IP address lookups and packet filtering. It enhances cache memory systems by speeding up tag matching for quick data retrieval. In AI and machine learning, it accelerates pattern matching algorithms, making it ideal for real-time processing. BCAM also plays a role in network security, enabling real-time packet filtering and intrusion detection. Additionally, it is applied in database search engines, image processing, and biomedical applications like DNA sequence matching for rapid data analysis.

## **IV. RESULTS**

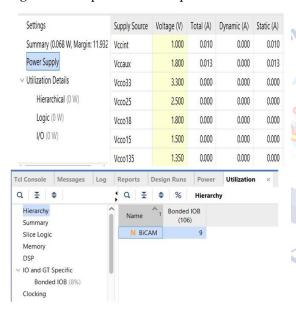

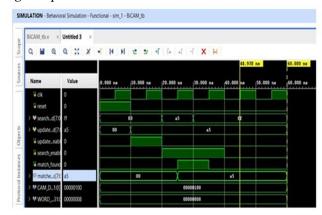

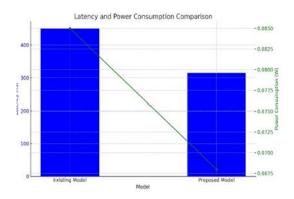

The simulation results of the proposed Binary Content Addressable Memory (BCAM) model demonstrate significant improvements in performance and efficiency.

Fig 2:Report Power

Fig 3:Latency and Power Consumption Graph

Fig 4: Simulation Waveform Output

## **V CONCLUSION**

The proposed BCAM model on FPGA successfully reduces search latency and power consumption while enhancing performance. The efficient mapping and updating algorithms enable faster and reliable data retrieval, making it suitable for high-speed applications.

## **FUTURE SCOPE**

- Implementing multi-level BCAM for further speed optimization.

- Exploring power-gating techniques to reduce power consumption.

- Enhancing scalability to support larger data sets.

# Conflict of interest statement

Authors declare that they do not have any conflict of interest.

# REFERENCES

- [1] XILINX INC. (2023). XILINX VIVADO DESIGN SUITE USER GUIDE.

- [2] J. PATEL ET AL., "FPGA-BASED CAM OPTIMIZATION FOR HIGH-SPEED NETWORKS," IEEE TRANSACTIONS ON VLSI, 2022.

- [3] S. KUMAR ET AL., "EFFICIENT CAM SEARCH TECHNIQUES FOR DATA RETRIEVAL," JOURNAL OF EMBEDDED SYSTEMS, 2021.